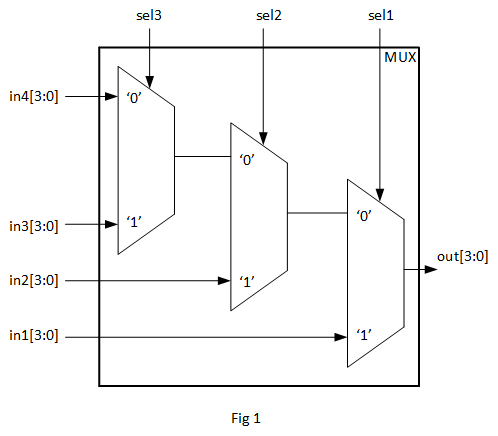

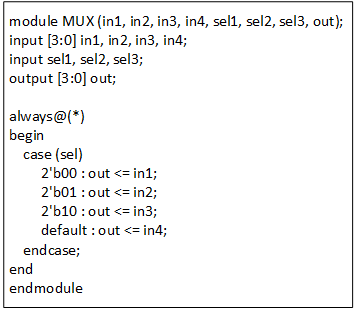

‘Case’ statements in verilog or VHDL are more efficient than using ‘if-else‘ statements for parallel processing of data because ‘if-else’ can generate long combinatorial chains (priority scheme) of logic that can cause difficulties meeting timing.

It is worth noting here that the options of the ‘case’ statement must be mutually exclusive and all possible input values of the control expression must be included in the set of options (ie no incomplete assignments) to avoid the inference of unintended latches.

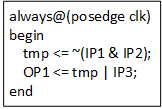

The following verilog code :

Will be synthesized to the following priority combinatorial logic :

All possible input values of the control expression must be included in the set of options (as shown above) to avoid the inference of unintended / accidental transparent latches.

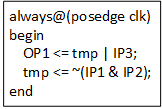

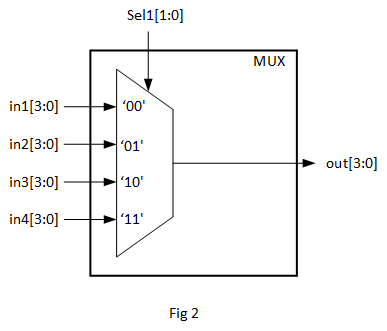

However, if we recode the above verilog code to the following, it will direct the synthesis tool to implement parallel logic (fig2) rather than a priority scheme (fig1).

This will be synthesized to one multiplexer :

If a priority encoder is required (eg designing a priority interrupt control logic) this can be coded by using the nested if-else statements but need to be cautious & make sure that it will pass timing during synthesis at the maximum operating frequency of interest otherwise it will require re-designing/re-coding to try to resolve the timing issues.